# **EMC2104**

# EMC2104 Silicon Errata and Data Sheet Clarification

#### TABLE 1: CHIP REVISION INFORMATION

| Device ID = 1DH     |                 |                             |

|---------------------|-----------------|-----------------------------|

| Functional Revision | Revision Number | Part Marking<br>(Note 1)    |

| В                   | 01h             | 2104-1<br>Lot Number<br>BCC |

| С                   | 02h             | 2104-1<br>Lot Number<br>CCC |

**Note 1:** The Functional Revision Letter is the first letter of the third line of the part marking printed on the top of the package.

#### TABLE 2:DATA SHEET REVISION INFORMATION

|    | Part Number     | Specification Type | Revision Number | Date       |

|----|-----------------|--------------------|-----------------|------------|

| 1. | EMC2104 (Rev B) | Data sheet         | v1.59           | 08/21/2007 |

| 2. | EMC2104 (Rev C) | Data sheet         | v1.60           | 08/27/2007 |

#### TABLE 3: ANOMALIES, SPECIFICATION CHANGES, AND ISSUES SUMMARY

| Туре          | Functional Rev<br>(Note 2) |   | Description                       |

|---------------|----------------------------|---|-----------------------------------|

|               | В                          | С |                                   |

| PWM1 Polarity | Х                          | Х | PWM1 Polarity Inverted            |

| Inverted      | Х                          | х | PWM1 Polarity Bit                 |

|               | Х                          | - | TRIP_SET not Detecting Open State |

|               | Х                          | - | Look Up Table Enable              |

|               | Х                          | - | Digital Pins Fail Latchup Test    |

|               | Х                          | - | SYS_SHDN# Leakage Current         |

|               | Х                          | - | Vdd Rise Time                     |

## TABLE 3: ANOMALIES, SPECIFICATION CHANGES, AND ISSUES SUMMARY (CONTINUED)

| Туре          | Functional Rev<br>(Note 2) |   | Description                          |

|---------------|----------------------------|---|--------------------------------------|

|               | В                          | С |                                      |

| Specification | -                          | Х | Default SpinUp Level                 |

| Changes       | -                          | Х | Tcrit Registers Added                |

|               | -                          | Х | New Hardware Failsafe Channel Option |

|               | Х                          | Х | GPIO Drive Current                   |

|               | -                          | Х | GAINP and GAINI Weight               |

| Issues        | -                          | - | No Issues                            |

2: 'X' = Indicates the Functional Rev which has the anomaly or in which a Specification Change was implemented; '-' = Not Applicable to the Functional Rev.

## Silicon Errata Issues

#### Errata 1: **PWM1** Polarity Inverted

The PWM1 output is inverted so it is logic high when in the fan OFF condition.

#### END USER IMPLICATIONS

This polarity inversion is opposite of the requirements for directly driving most 4-wire fans.

#### Work Around

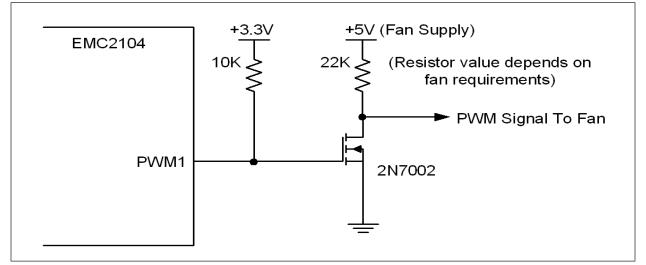

A signal inversion must be added. A typical circuit is shown in Figure 1.

| FIGURE 1: P | VM DRIVE SIGNAL INVERSION |

|-------------|---------------------------|

|-------------|---------------------------|

#### Errata 2: PWM1 Polarity Bit

#### DESCRIPTION

Register 0x2A, bit 0 does not control the PWM1 polarity as specified.

#### END USER IMPLICATIONS

The polarity of PWM1 cannot be changed.

#### Work Around

The external drive circuit must provide any polarity inversions required by the application.

#### Errata 3: TRIP\_SET not Detecting Open State

#### DESCRIPTION

The TRIP SET pin is not detecting an "OPEN" condition.

#### END USER IMPLICATIONS

This anomaly will set the  $T_{TRIP}$  value to the maximum temperature available (122C or 154C) if a resistor is not in place. This "OPEN" condition is not a desired condition, but rather a fail safe for manufacturing defects in the resistor or assembly of the final product.

#### Work Around

If the minimum temperature for T<sub>TRIP</sub> (60C or 92C) is desired, a short to ground is required. This anomaly will be corrected in Functional Revision C.

#### Errata 4: Look Up Table Enable

#### DESCRIPTION

When enabling LUT1 or LUT2, the corresponding fan output will enter spinup regardless of current fan setting.

#### END USER IMPLICATIONS

The fan will have a noticeable surge anytime the respective look up table is enabled.

#### Work Around

This anomaly will be corrected in Functional Revision C.

#### Errata 5: Digital Pins Fail Latchup Test

#### DESCRIPTION

The digital I/O pins fail Latchup Testing. The pins affected include pin 5 through pin 16: OVERT3#/GPIO5/PWM4, ALERT#, CLK\_IN/GPIO1, OVERT2#/GPIO4/PWM3, SYS\_SHDN#, SMDATA, SMCLK, GPIO6, PWM2/GPIO3, TACH2/GPIO2, TACH1, and OVERT1#/PWM1.

To cause latchup on these pins, the input signal needs to be pulled below ground and greater than 20mA must be drawn from the pin; the specification for this test requires the pin to withstand greater than 150mA.

#### END USER IMPLICATIONS

If this event occurs, power-cycling is required to restore normal operation. However, it is not expected that such a signal can be generated on actual application boards.

#### Work Around

This anomaly will be corrected in Functional Revision C.

#### Errata 6: SYS\_SHDN# Leakage Current

#### DESCRIPTION

The leakage current when Vdd=0 is greater than specified. If SYS\_SHDN# is pulled up to a voltage of 3-5Vdc when the supply pin Vdd = 0, the leakage current can be up to 30uA. The leakage current increases with voltage and temperature.

#### END USER IMPLICATIONS

This anomaly may result in an undesirable power consumption and voltage drop across the pullup resistor.

#### Work Around

This anomaly will be corrected in Functional Revision C. To minimize the leakage current, use the lowest pullup voltage possible.

#### Errata 7: Vdd Rise Time

#### DESCRIPTION

Some Vdd rise times (also called supply ramp rate) may result in improper internal initialization. The susceptible rise times vary from part to part and somewhat with temperature so it is not possible to specify a maximum rise time for correct operation.

#### END USER IMPLICATIONS

The EMC2104 will be inoperable if this anomaly occurs. It will not be damaged and cycling power may restore proper operation.

#### Work Around

This anomaly is corrected in Functional Revision C. As a workaround, decreasing the Vdd rise time generally results in normal operation.

## **Specification Changes**

The Specification Changes described below are detailed in Data Sheet V1.60, dated 8-27-07.

#### DEFAULT SPINUP LEVEL

The default SpinUp Level is changed from 30% to 60% in Functional Revision C. Some fans, especially when driven by linear drive circuits cannot start at 30%. The higher default SpinUp Level will reduce the possibility of repeated SpinUp routine executions. The programmer can simply set the SpinUp Level to the required value with Functional Revision B; changing the default will reduce confusion due to the fan not starting properly.

#### TCRIT REGISTERS ADDED

To increase the flexibility of the software-programmed temperature channels that can trigger SYS\_SHDN#, independent Tcrit Limit and Status registers will be added in Functional Revision C. These limits are "Write-Once and Lock" and cannot be changed once written. If these limits are exceeded, the SYS\_SHDN# pin will be asserted. Operation is similar to setting the SYSx bits in configuration register 20h, but utilizes independent Tcrit Limit Registers for added flexibility, allowing the temperature channels' high and low limits to assert the ALERT# pin without triggering the SYS\_SHDN# pin.

#### NEW HARDWARE FAILSAFE CHANNEL OPTION

To permit the Internal temperature channel to be used as the hardware-programmed channel, an additional option will be added in Functional Revision C. The SHDN\_SEL pin's decode options will be modified so that the Internal channel can be used as the hardware-programmed channel.

The "Disabled" decode selection will be re-deployed as the Internal Temperature hardware-strapped option.

The behavior of the TRIP\_SET input is different in this mode. While the TRIP\_SET voltage setting can normally be created with a single resistor to ground, when the internal temperature channel is selected a resistor divider is required. Consult the data sheet for the formula which describes this resistor divider.

#### **GPIO DRIVE CURRENT**

The Voh specification of Vcc-0.4V is marginal at 8mA. The drive current value will be changed to 4mA.

#### GAINP AND GAINI WEIGHT

The weight of the Proportional and Integral Gains factors have been modified in Revision C. GAINP is increased by x2, while GAINI is decreased by X4. This change can increase the responsiveness when fast changes are needed. It does not affect applications where Ramp Rate Control is employed, i.e. the step size is limited.

#### Issues

NO ISSUES

## APPENDIX A: DOCUMENT REVISION HISTORY

| Revision Level   | Description                                                                 |

|------------------|-----------------------------------------------------------------------------|

| REV A (03-11-14) | REV A replaces previous SMSC version v0.92 (10/31/07)                       |

| v0.92 (10/31/07) | Added Vdd Rise Time anomaly and GAINI and GAINP Weight Specification Change |

| v0.91 (09/25/07) | Clarified Data Sheet Revisions, cosmetic chgs                               |

| v0.9 (09/10/07)  | Initial Release for Engineering Review                                      |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

flexPWR, JukeBlox, Kleer, KleerNet, MediaLB, and MOST

The preceding is a non-exhaustive list of trademarks in use in the US and other countries. For a complete list of trademarks, email a request to <a href="mailto:legal.department@microchip.com">legal.department@microchip.com</a>. The absence of a trademark (name, logo, etc.) from the list does not constitute a waiver of any intellectual property rights that SMSC has established in any of its trademarks.

All other trademarks mentioned herein are property of their respective companies.

© 2014, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 9781620779798

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV — ISO/TS 16949—

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

10/28/13